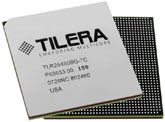

Compania americana Tilera, fondata de profesorul Anat Agarwal de la MIT, va incepe in aceasta perioada comercializarea unor procesoare cu 64 nuclee. Acestea au primit numele de Tile64, si reprezinta, conform creatorilor, prima schimbare arhitecturala semnificativa a ultimului deceniu.

Compania americana Tilera, fondata de profesorul Anat Agarwal de la MIT, va incepe in aceasta perioada comercializarea unor procesoare cu 64 nuclee. Acestea au primit numele de Tile64, si reprezinta, conform creatorilor, prima schimbare arhitecturala semnificativa a ultimului deceniu.

Tile64 este realizat pe un sistem parcelar (de unde si numele), cu 64 de parcele. Fiecare parcela acomodeaza un core, memoria cache proprie, si un comunicator. Aceasta configuratie a fost gandita de profesorul Anat Agarwal in urma cu aproximativ 10 ani, si a durat pana acum pentru a ajunge pe piata.

Fiecare core are cate trei unitati de procesare, doua ALU (Arithmetic Logic Unit) si o FPU (Floating Point Unit), si frecvente intre 600 si 900 MHz. Memoria cache este impartita in 16 KB L1 cache exclusiv si inca 64 KB L2 cache per core. Insa cache-ul L2 functioneaza la comun pentru cele 64 nuclee, ducandu-se la 4 MB L2 cache total si comun.

Fiecare Tile64 are integrate patru controller-e de memorie DDR2, doua interfete 10-GigaLAN, doua interfete GigaLAN, doua interfete PCI-E 4x si o interfata I/O modulabila. Din toate acestea, ne putem da seama ca Tile64 nu are nevoie nici de un northbridge, nici de un southbridge. Este o solutie single chip. Si cu toate acestea consuma intre 11 si 19 W doar (170 – 300 mW per core). In plus, Tile64 isi poate trece core-urile nefolosite in sleep mode, petru a scadea si mai mult concursul.

Aceste procesoare sunt fabricate de TSMC, intr-un proces tehnologic de 90 nm (din motive financiare), vin sub forma unor placi PCI-E si costa 435 $ pentru cantitati de minim 10 000 unitati. Ele exceleaza in procesare de retea avansata si procesare video, dar pot fi pana la urma folosite in orice scop.

Sustine blogul cumparand prin linkurile afiliate, fără vreun cost suplimentar pentru tine:

Sustine blogul cumparand prin linkurile afiliate, fără vreun cost suplimentar pentru tine: